雷锋网注:【 图片来源:Intel Newsroom所有者:Ramune Nagisetty 】

小芯片(chiplet)的问世被当成一种标志:人们试图增强计算机的系统性能,尽管传统的摩尔定律已经接近尾声。

支持者认为,小芯片的应用不仅会催生更为专业的系统,还会给芯片行业带来更高的产量。更重要的是,这可能会促使无晶圆厂半导体行业发生重大转变,推动这一行业的最终产品变成小型专用芯片,而这种芯片会与通用处理器以及其他芯片组合在一起。

英特尔在俄勒冈州有一个技术开发小组,Ramune Nagisetty担任该小组的首席工程师,她一直致力于帮助全行业建立小芯片生态系统。今年三月,Ramune Nagisetty接受了IEEE Spectrum的专访。

本文中,Ramune Nagisetty就以下几个方面作出了回答:

1.Chiplet的定义及重要性

2.英特尔的EMIB和应用

3.存在的问题和行业标准

4.对未来的展望

谈到“chiplet”这一概念的界定以及它的重要性时,Ramune Nagisetty表示:

从实际上来说,“chiplet”是一种芯片,封装了一个IP(知识产权)子系统。它通常是通过高级封装集成,或者是通过标准化接口使用。至于它们为什么会变得如此重要,这是因为我们的计算和工作类型呈爆炸式增长,目前没有一种全能的办法来应对这些问题。从根本上说,对一流技术的异构集成是延续摩尔定律的一种方式。

Nagisetty认为,异构技术并不是非要硅来完成,它还可以应用其他类型的半导体,例如,锗或III-Vs。当然,未来我们会有更多种类的半导体技术。虽然,目前我们只有基于硅的小芯片,但它们能够应用在不同的技术里。它们还可以在数字、模拟、RF以及内存技术等不同的领域进行调优以获得更好的性能。在这方面,真正的驱动力是存储器的集成。高带宽存储器(HBM)本质上是异构硅封装集成的第一个证明,而内存器本质上是第一种异构集成类型。

那么,英特尔连接小芯片的EMIB(嵌入式多芯片互连桥)是什么,它是如何运转的呢?Nagisetty表示:

我们可以把它看作是连接两个芯片的高密度桥梁,这大概是理解EMIB的最好方式。我想,很多人都悉知使用硅介体来作高级封装衬底的用途,因为它具有紧密的互连性和内置硅穿孔,这让芯片之间的高带宽连接成为可能。

EMIB(图中圆圈所示)使用高密度互连连接到同一封装内的芯片

将芯片连接到EMIB的连接凸块比普通凸块(左下)具有更精细的间距

雷锋网注:【 图片来源:IEEE所有者:Intel 】

EMIB本质上就是一个非常小的硅介体,它具有非常高密度的互连性。而所谓的微凸块是连接芯片与芯片的焊料小球,它的密度比标准封装衬底要高得多。EMIB一般都会被嵌到一个标准封装衬底中。使用EMIB,你就可以在需要的地方实现最高互连密度,然后再使用一个标准的封装衬底来完成剩下的互连。

这样做有很多好处,其中之一就是节约成本,因为硅介体的成本与面积成正比。在这种情况下,我们能将高密度互连定位到最需要的地方。此外,使用标准的封装衬底而不是硅介体,在整体嵌入损耗(由于材料特性导致的信号衰减)方面也有好处。

对于英特尔使用EMIB的目的,Nagisetty是这样解释的:

英特尔已经展示了几个关于小芯片的应用,虽然其中有两种基于EMIB技术,但它们非常不同。

第一个是Kaby Lake-G,这是我们将AMD的Radeon GPU和HBM与我们自己的CPU芯片集成而来的。我们使用EMIB集成GPU和HBM。然后我们再通过封装内的PCI Express(一个标准的电路板接口)集成GPU和CPU。

这个产品的真正有趣之处在于,我们使用不同厂商的元件和共同的行业标准接口(HBM和PCI Express)来创建一流的产品。在本例中,我们使用了一个组件(GPU和HBM),该组件能够单独放在一块板上,然后集成封装。而PCI Express可以用于远距离发送信号,这更像是典型的电路板。将它封装起来并不是一个最优的解决方案,但它的速度够快。

除了Kaby Lake-G,Nagisetty接下来要讨论的是Stratix 10 FPGA:

Stratix 10的中心是英特尔的FPGA,被六个小芯片包围,其中四个是高速收发芯片,两个是高带宽内存芯片,它们都被封装在一起。这个产品集成了三个厂商贡献的六种技术,进一步证明了不同厂商之间的互用性。

Stratix 10 FPGA使用了行业标准的模对模接口AIB,这是英特尔的高级接口总线。它是为这个产品创建的,算得上是一个行业标准,用于封装内的高带宽、逻辑到逻辑互连。所以,HBM是内存集成的第一个标准,AIB是逻辑集成的第一个标准。

英特尔Stratix 10是使用EMIB连接封装中小芯片的主要示例

雷锋网注:【 图片来源:IEEE所有者:Intel 】

作为这个生态系统的中心,AIB接口和FPGA真正伟大之处在于可行的混合匹配模式。目前,许多公司和大学也实施了DARPA的CHIPS(通用异种基因集成和IP重用策略),利用AIB来创建小芯片。

Nagisetty想谈的第三个例子是英特尔的Foveros,她说:

这是我们逻辑对逻辑的模堆积,去年十二月我们首次谈及了这项技术。在1月份的CES上,我们发布了相关产品 Lakefield。虽然它由小芯片集成,但不是水平叠堆,而是垂直叠堆。

这种类型的集成可以在两个芯片之间获得极高的带宽。但它基于内部的专有的接口,而且这两个芯片基本上要进行同步设计的,以便管理电力输送和散热等问题。

就逻辑对逻辑的模堆积而言,行业内标准的出现可能还需要很长的时间,因为模基本上是共同设计的。建立在逻辑之上的存储堆积可能是三维堆积标准诞生的地方。

Nagisetty还强调,设计堆叠芯片时,重点要考虑散热问题:

不难想象,叠模会加剧发热的问题,所以我们要仔细设计板面来应对发热情况。我们还需要考虑整个系统的体系结构。3D堆叠的应用含义将影响架构决策,不仅是物理架构,而是整个CPU或GPU和系统架构。

此外,如果我们想要展现任何互用性,我们就需要有互用的材料系统。为了实现互用性,我们需要做大量的工作,但是我认为,散热是最大的挑战,电源交付和电源管理紧随其后。

除了上述问题,建立测试的行业标准也非常重要。

通常,我们会使用封装完毕的部件进行测试。所以,我们必须把正常运作的小芯片封装起来,这样我们就不会因错误地封装了有问题的小芯片,而导致产量下降。因此,我们要想出一个完美的测试策略。另外,我们还需要供应商对电力和热力的大力支持。这意味着我们要连接所有集成的芯片,以便同时管理电源和热量。

就电气可操作性而言,我们去年7月发布的接口AIB,实际只是一个物理级的标准,即电气和物理接口。所以,我们还需要有贯穿上层协议的标准。

最后一个标准是机械标准,这一点很明显。实际上,微凸块的放置和块与块之间的路径需要相关的行业标准来保证互用性。

想要了解一个小芯片是否能够正常运作,通常要对封装部件进行热测试。因此,我们必须在芯片封装之前测试裸模芯片。测试封装的部件,或者为封装部件输送电力会相对简单,而在裸模上进行测试会遇到更多挑战,因为测试需要额外设计测试探头。

另一件事是,为了测试独立小芯片而需要的东西都需要设计到芯片中,小芯片必须在封装前单独完成测试,这是非常重要的。因为,如果封装好的芯片里有损坏品,就会浪费一同封装的好芯片。

这种芯片确实大幅提升了产量,但这只是我们使用它的一个原因,而且不是唯一的原因。产量提高的关键因素是在封装前测试这些芯片。

这种芯片还会改变事物的设计方式,高带宽内存集成就是一个例子。目前,高宽带内存已经在GPU和高性能AI处理器中广泛使用。目前看来,小芯片和内存集成已经改变了芯片的设计和集成方式。

小芯片的协同设计无疑是一个重要的发展领域。我认为,未来,将有不少供应商提供这种小芯片。理解不同芯片供应商的需求,并跨边界进行通信,这一步非常重要。

小芯片的问世及使用只是一场革命的开始,一个新的产业生态系统将围绕这一点发展。它将改变我们设计芯片或封装部件的方式,改变半导体生态系统的演变。

关于这个新的生态系统,Nagisetty十分乐观:

我认为这对于无晶圆厂初创公司来说是一个非常激动人心的时刻,因为他们有机会创建更小的IP子系统。当它使用小芯片集成时,这个子系统将非常有价值。

DARPA芯片项目的目标之一是,支持知识产权的再利用,并降低生产产品过程中的非经常性工程成本总量。小芯片的出现允许无晶圆厂的初创公司专注于自己非常擅长的IP部分,而不必担心其他内容。

小芯片的发展不仅对无晶圆厂初创公司有所助力,它在DARPA资助的电子复兴计划里也占据着重要地位。虽然,有能力研发高端半导体技术的公司数量在过去几年有所下降,中小企业的创新能力也受到了影响,但这对于无晶圆厂的初创企业来说,是乘势而上的绝佳机会。

在这一领域将诞生一个创新的平台,很多变化会从这里开始,很多机会也蕴藏在这里。

为了促进这种基于加速器和封装集成的新型生态系统的发展,有很多事情正在快速发生。我们并不能算出这场革命还要多久才会到来,但我应该不会花太长时间了,或许就在近些年。

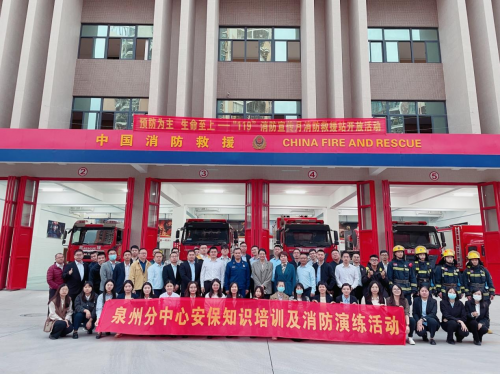

英特尔目前在市场上投放的产品都是尖端例子,可以教我们如何在未来创造新产品。我们虽然有很多集成方案,但才刚刚开始朝这个方向发展。不过,有了这些技术,我们确实有能力比后来人取得更大的进步。